# **ASIC Design of ReRAM-based AI Accelerators**

Design Document

sdmay25-19 Client: Henry Duwe Advisors: Henry Duwe & Cheng Wang

Team Members/Roles: Sam Burns (Mixed Signal designer), Travis Jakl (Mixed Signal Designer), Noah Mack (Digital Signal Designer), & Olivia Price (Analog Signal Designer)

sdmay25-19@iastate.edu http://sdmay25-19.sd.ece.iastate.edu/

## **Executive Summary**

Matrix-vector multiplication (MVM) is a fundamental operation in many computing tasks, yet performing it in traditional systems is inefficient due to frequent data transfers between memory and the arithmetic logic unit (ALU). One promising solution is to perform computation in memory (e.g., ReRAM) using the memory array itself. Such computational memories are an active area of research but have challenges associated with the analog nature of their computation. Our project focuses on implementing a test vehicle for computational ReRAM and constituent analog components

The key requirement for this project is to have four unique ReRAM architectures that can be tested individually on a test chip. Two designs were inherited from past student groups, and our team developed two additional architectures. The first design reorients the ReRAM cell structure by aligning the word line and the source line, which may improve routing efficiency and layout density. The second design eliminates the transistors creating a true crossbar that consists of just memristor which could help scalability, but introduce challenges such as sneak path current.

All designs utilize the Skywater 130nm process and the components are implemented using open-source tools including Xschem, Magic, and Ngpice. In addition to circuit and layout design, we are developing C-code for a microcontroller to interface with each ReRAM cell, allowing analysis testing and performance evaluation of the different architectures.

The progress made in the first semester included learning how to utilize the tools to our given criteria, researching the ReRAM technology and how to implement it, and creating two new unique designs to go into our research chip. By the end of the first semester, we had four distinct ReRAM designs planned and partially implemented. We also learned how to use the tools so our designs can be tested, fabricated, and placed on the project wrapper when they are prepared.

The second semester focused on implementing our designs using open-source tools and thoroughly testing each to ensure proper functionality. We also developed C code to interface with a microcontroller, enabling performance comparisons between the different ReRAM architectures. Extensive testing was conducted, layouts were completed, and three out of the four designs reached final layout status.

However, during the second semester an unexpected shutdown of Efabless fabrication removed our ability to perform pre-check, tapeout check, and to submit the chip for fabrication. In response, we shifted our focus to completing the simulation, validation, and the documentation process. Despite this change, we met the project's primary objectives: to create, test, and compare four unique ReRAM architectures using an open-source workflow.

Next steps include finding a new company to fabricate our design, completing functional verification of designs, finalizing the MCU codebase for automated MVM testing, and publishing detailed documentation. This project demonstrates the viability of ReRAM for in-memory computation and lays the groundwork for future research into low-power, high efficiency artificial intelligence.

## **Learning Summary**

## **Development Standards & Practices Used**

Below is a bulleted list of our circuit and hardware design practices. Also listed is the software that we are using to implement our designs and the engineering standards we have been following.

Circuit Design Practices:

- Analog and digital circuit integration

- Noise management

- Timing analysis

- Simulation and validation

- Device sizing and parameter optimization

Hardware Design Practices:

- Design for fabrication

- ReRAM-specific design considerations

Software Practices:

- Xschem (circuit design software)

- Magic (layout design software)

- Ngspice (simulation software)

Engineering standards:

- *IEEE 1481-2019- IEEE Standard for Integrated Circuit (IC) Open Library Architecture (OLA)*: This is applicable to our project since it specifies how our integrated circuit should be examined using a variety of design automation tools for timing and power consumption.

- *IEEE 1076.4-2000- IEEE Standard VITAL ASIC Modeling Specification*: This standard is relevant to our project because it calls for the testing of an ASIC chip using extremely precise and effective simulation models.

- *IEEE 1149.4-2010- IEEE Standard for a Mixed-Signal Test Bus*: This is relevant to our project since it will have both digital and analog components, and we will need to properly test each one separately and in tandem.

• *IEEE 1364-2005- IEEE Standard for Verilog Hardware Description Language*: Since our project requires us to create Verilog code to facilitate communication between the wrapper and the analog portion, this standard is appropriate for us.

## **Summary of Requirements**

- Four different ReRAM compute crossbar architectures must be present in the final tape-out.

- Component circuits are individually characterizable and accessible through analog pins.

- Uncertainty evaluation on architectures being implemented; the difference between simulated ideal crossbar current and actual within one ADC step.

- C Code for the MCU to interface with the ReRAM that enables testing and demonstrates that the ReRAM can compute an MVM within an epsilon tolerance.

- Bring up Documentation for FORMing the ReRAM Cells and characterizing the component circuitry via individual test benches.

## **Updated Summary of Requirements**

We provided an updated summary of requirements due to efabless shutting down. This shows what is not attainable after the shutdown.

- Component circuits are individually characterizable and accessible through analog pins.

- Four different ReRAM compute crossbar architectures must be present in the final top level design and layout.

- C Code for the MCU to interface with the ReRAM that enables testing and demonstrates that the ReRAM can compute an MVM within an epsilon tolerance.

- Bring up Documentation for FORMing the ReRAM Cells and characterizing the component circuitry via individual test benches.

## Applicable Courses from Iowa State University Curriculum

- EE 330 Integrated Electronics

- EE 465 Digital VLSI Design

- EE 435 Analog VLSI Circuit Design

- EE 501 Analog and Mixed-Signal VLSI Circuit Design Techniques

- CPR E 281 Digital Logic

- CPR E 288 Embedded Systems I: Introduction

- CPR E 381 Computer Organization and Assembly Level Programming

## New Skills/Knowledge acquired that was not taught in courses

- ReRAM technology

- Hierarchical analog design

- Compute in memory design and application

- Open-source software: Xschem, Magic, Ngspice

- Skywater 130nm process

- Tape-out process of silicon chips

# **Table of Contents**

| Executive Summary                                                         | 2  |

|---------------------------------------------------------------------------|----|

| Learning Summary                                                          |    |

| Development Standards & Practices Used                                    |    |

| Summary of Requirements                                                   | 4  |

| Updated Summary of Requirements                                           | 4  |

| Applicable Courses from Iowa State University Curriculum                  | 4  |

| New Skills/Knowledge acquired that was not taught in courses              | 5  |

| List of Figures/Tables/Definitions                                        | 8  |

| Figures                                                                   |    |

| Tables                                                                    | 9  |

| Definitions                                                               | 9  |

| 1. Introduction                                                           | 10 |

| 1.1 Problem Statement                                                     | 10 |

| 1.2 Users and User Needs                                                  | 10 |

| 1.3 What is ReRAM?                                                        | 10 |

| 2. Requirements, Constraints, and Standards                               |    |

| 2.1 Requirements                                                          | 11 |

| 2.2 Constraints                                                           | 11 |

| 2.3 IEEE Standards                                                        | 11 |

| 2.4 Applicable Courses From ISU Curriculum                                |    |

| 3. Project Plan                                                           |    |

| 3.1 Project Management/Tracking Procedures                                | 12 |

| 3.2 Task Decomposition                                                    |    |

| 3.3 Project Proposed Milestones, Metrics, and Evaluation Criteria         | 13 |

| 3.4 Project Timeline/Schedule                                             |    |

| 3.5 Risks and Risk Management/Mitigation                                  |    |

| 3.5.1 Updated Risks and Risk Management/Mitigation Post Efabless-Shutdown | 14 |

| 3.6 Personnel Effort Requirements                                         |    |

| 3.7 Other Resource Requirements                                           | 16 |

| 4. Design                                                                 |    |

| 4.1 Broader Context                                                       |    |

| 4.1.1 Broader context                                                     | 17 |

| 4.1.2 Prior Work/Solutions                                                |    |

| 4.1.3 Technical Complexity                                                | 19 |

| 4.2 Design Exploration                                                    |    |

| 4.2.1 Design Decisions                                                    |    |

| 4.2.2 Ideation                                                            |    |

| 4.2.3 Decision-Making and Trade-off                      |    |

|----------------------------------------------------------|----|

| 4.3 Proposed Design                                      |    |

| 4.3.1 Overview                                           |    |

| 4.3.2 Detailed Design and Visuals                        | 22 |

| 4.3.3 Functionality                                      |    |

| 4.3.4 Areas of Concern and Development                   |    |

| 4.4 Technology Considerations                            |    |

| 5. Testing                                               |    |

| 5.1 Unit Testing                                         |    |

| 5.2 Interface Testing                                    |    |

| 5.3 Integration Testing                                  |    |

| 5.4 System Testing                                       |    |

| 5.5 Regression Testing                                   |    |

| 5.6 Acceptance Testing                                   |    |

| 5.7 User Testing                                         |    |

| 5.8 Security Testing                                     |    |

| 5.9 Results                                              |    |

| 6. Implementation                                        | 41 |

| 6.1 Design Analysis                                      | 41 |

| 7. Ethics and Professional Responsibilities              |    |

| 7.1 Areas of Professional Responsibility/Codes of Ethics |    |

| 7.2 Four Principles                                      |    |

| 7.3 Virtues                                              |    |

| 7.4 Ethics and Virtue Changes Throughout the Project     |    |

| 8. Closing Material                                      |    |

| 8.1 Conclusions                                          |    |

| 8.2 Value Provided                                       |    |

| 8.3 Next Steps                                           | 51 |

| 9. References                                            |    |

| 10. Appendices                                           |    |

| 10.1 Operation Manual                                    |    |

| 10.2 Alternative/Initial Versions of Design              |    |

| 10.3 Other Considerations if applicable                  |    |

| 10.4 Code                                                |    |

| 10.5 Team Contract                                       |    |

## List of Figures/Tables/Definitions

### Figures

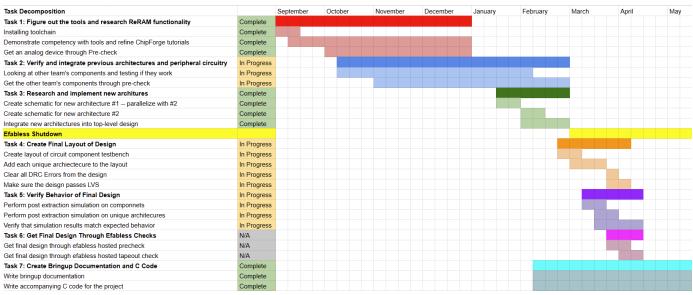

Figure 3.1: Gantt chart, page 14

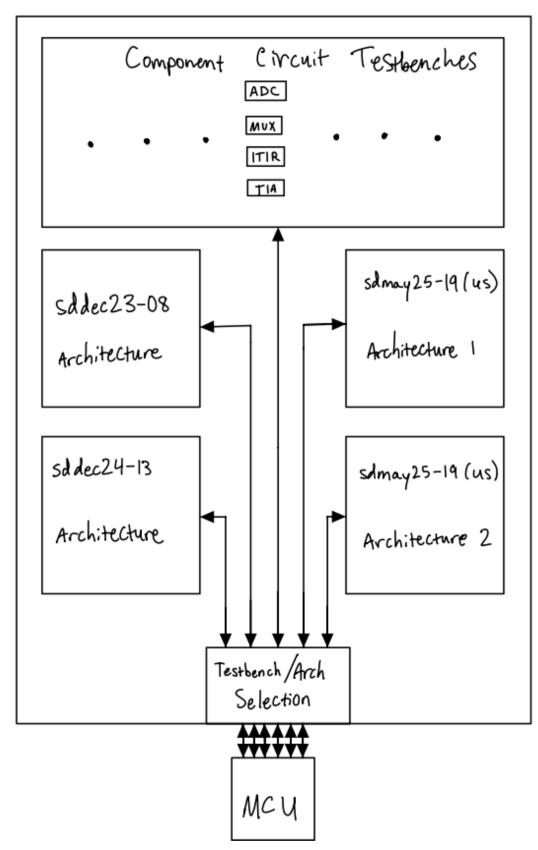

Figure 4.1: Top level block design, page 23

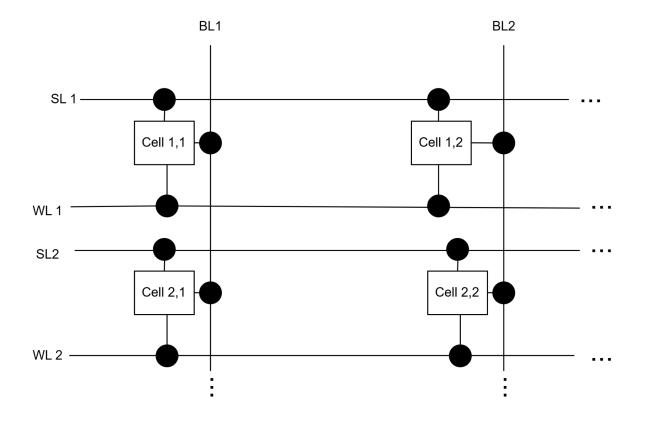

Figure 4.2: Schematic for one ReRAM crossbar architecture, page 24

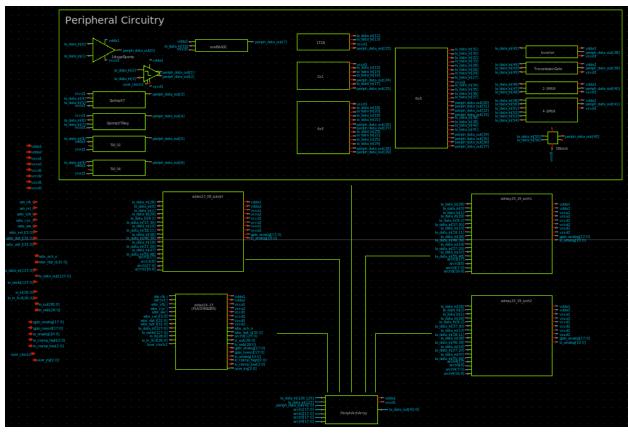

Figure 4.3: Schematic for our final top level design, page 25

Figure 4.4: Architectures from SDDec38-08 and SDDec24-13 in our top level design, page 26

Figure 4.5: Both architectures from this team in top level design, page 27

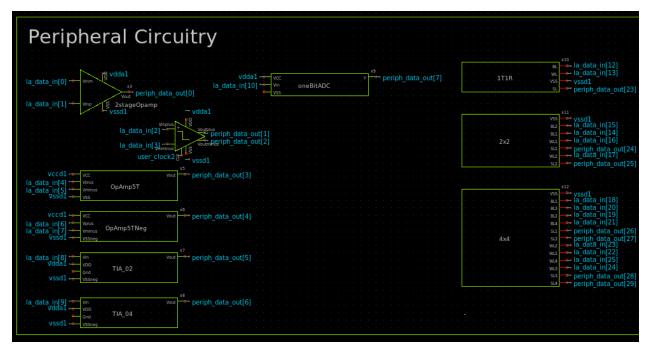

Figure 4.6: Peripheral circuitry in our top level design, page 28

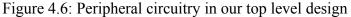

Figure 4.7: Peripheral circuitry in our top level design (cont.), page 28

Figure 4.8: Architecture select MUX outputting to MCU, page 29

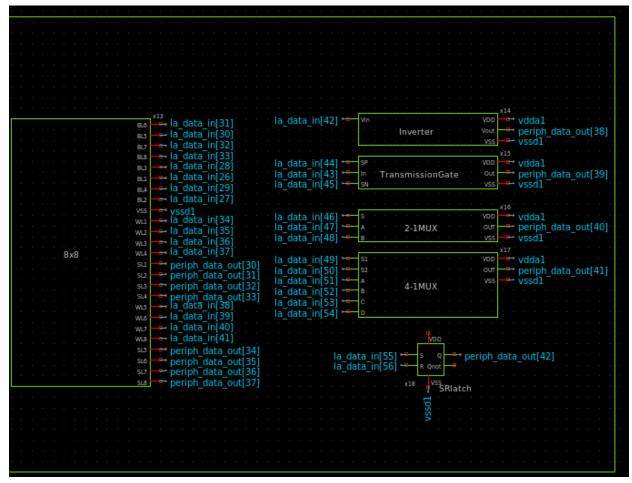

Figure 4.9: Our architecture one final layout, page 30

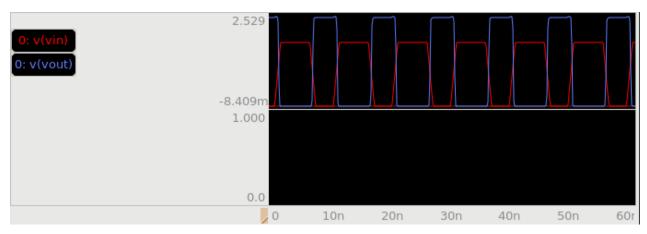

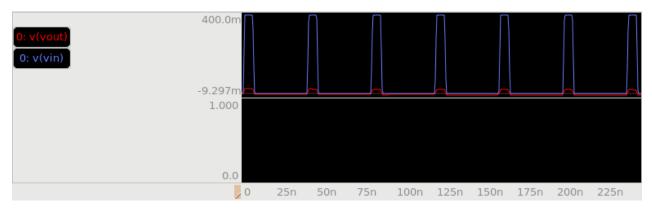

Figure 5.1: Simulation results from inverter, pre-layout, page 34

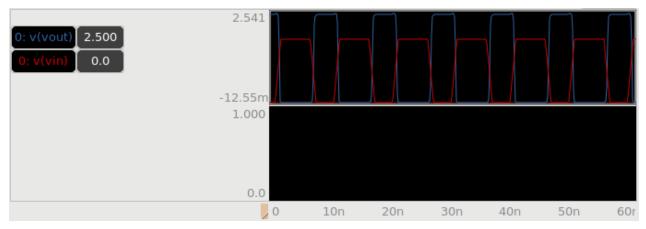

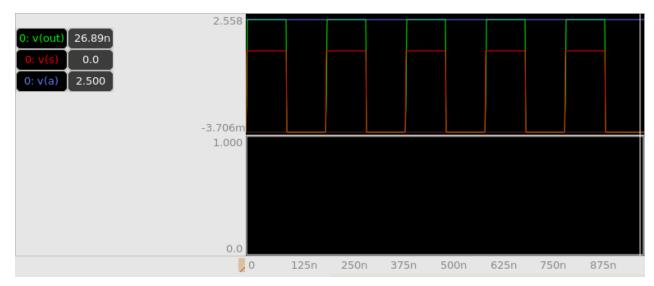

Figure 5.2: Simulation results from inverter, post-layout, page 35

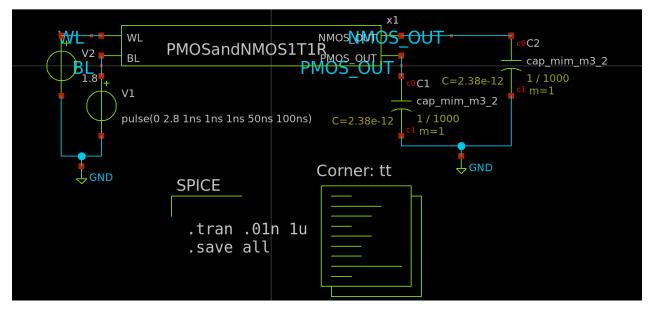

Figure 5.3: Testbench for comparing 1T1R cells using PMOS and NMOS transistors, page 35

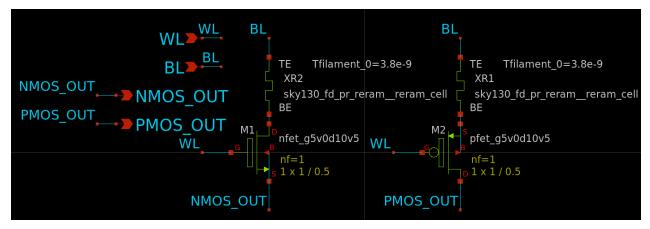

Figure 5.4: Schematic including two 1T1R cells, one using a PMOS transistor and the other using an NMOS transistor, page 36

Figure 5.5: Resulting waveforms from buffer testbench from team sddec23-08, page 36

Figure 5.6: Resulting waveforms from 2-to-1 multiplexer testbench from team sddec23-08, page 37

Figure 5.7: Resulting waveforms from 4-to-1 multiplexer testbench from team sddec23-08, page 37

Figure 5.8: Resulting waveforms from transmission gate testbench from team sddec23-08, page 38

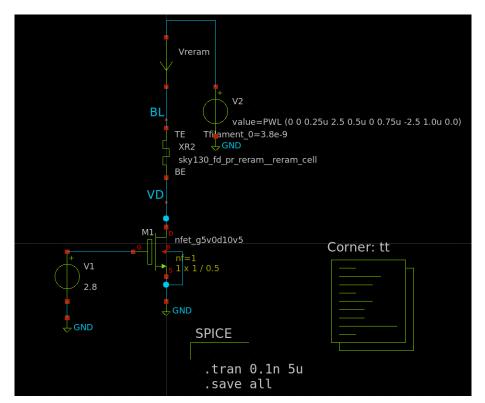

Figure 5.9: 1T1R testbench, page 38

Figure 5.10: Waveforms from our 1T1R testbench, page 39

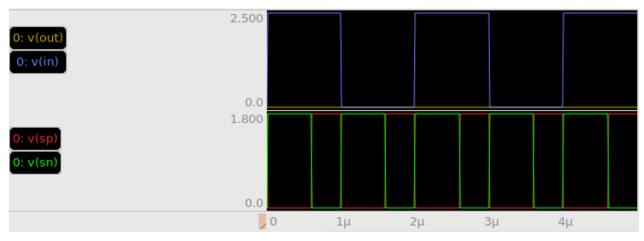

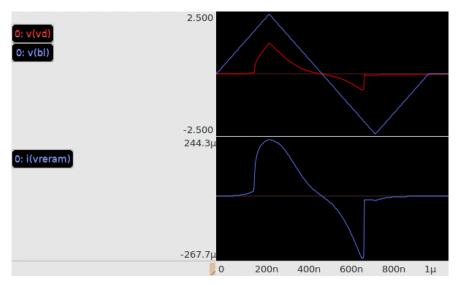

Figure 5.11: Transimpedance schematics testbench, page 39

Figure 5.12: Resulting waveform for a transimpedance amplifier, page 40

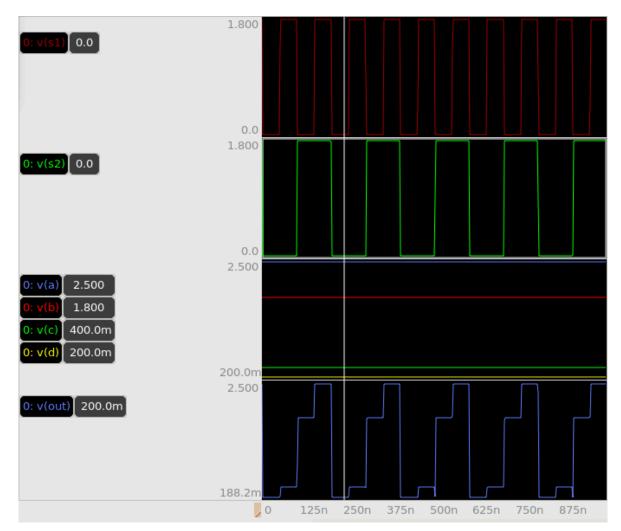

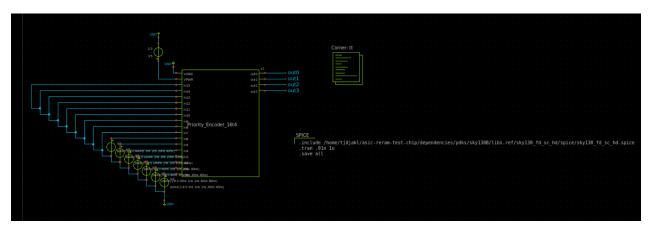

Figure 5.13: Priority Encoder testbench, page 40

Figure 5.14: Resulting waveform from our priority encoder, page 40

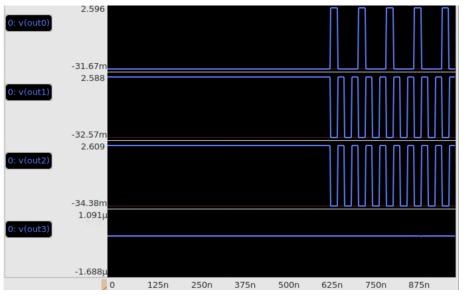

Figure 6.1: (a) Parallel Bitline and Sourcelines. (b) True Crossbar Design (both extracted directly from [6]), page 42

Figure 10.1: Top Level Schematic, page 53

Figure 10.2: explains ReRAM structural and operation basics and is extracted directly from [10], page 59

Figure 10.3: explains ReRAM state change requirements and is extracted directly from [5], page 59

Figure 10.4: Magic interface showing Devices 1 & 2 menu with proper vias, page 61

Figure 10.5: Layout showing correct VDD pin connections, page 62

Figure 10.6: LVS result indicating symbol issue, page 63

Figure 10.7: Klayout highlighting a DRC error at specified coordinates, page 64

Figure 10.8: LVS output indicating file path error, page 65

Figure 10.9: Commented lines within .spice file to be removed, page 66

#### **Tables**

- Table 3.1: Personnel effort requirements, page 15

- Table 4.1: Broader context, page 17

- Table 4.2: Pros/Cons of prior work/solutions, page 18

- Table 4.3: Comparing ADC architectures, page 21

- Table 4.4: Comparing ReRAM crossbar architectures, page 22

- Table 7.1: Codes of ethics, page 44

- Table 7.2: Four principles, page 46

- Table 10.1: Pinout, page 55

- Table 10.2: Skill sets covered by team, page 81

### Definitions

ReRAM: Resistive Random Access Memory 1T1R: ReRAM cell consisting of 1 transistor and 1 memristor ADC: Analog to Digital Converter XSchem: Open-source schematic creation software

Magic: Open-source layout creation software

Ngspice: Open-source analog simulation software

Gaw: Open-source analog waveform viewer

## **1. Introduction**

### **1.1 Problem Statement**

Matrix-vector multiplication (MVM) is one of the most common operations in machine learning applications. Performing MVM requires many multiply and accumulate operations, which takes a lot of time and energy in a typical CPU. Moving the required data back and forth in between the CPU and memory consumes a lot of energy in a traditional system. Compute-in-memory (CIM) technologies pose a potential solution to speeding up these processes by eliminating the memory bottleneck and allowing for parallel computation. ReRAM is an emerging, low-power, and non-volatile memory technology which may be used for CIM. Using ReRAM for CIM may require a rethink of ReRAM architectures. First, there is significant potential for impact from noise, both from the internal architecture of the ReRAM matrix as well as device noise from other chip components. Second, there are limited opportunities for ReRAM chip fabrication. For these reasons, we will design a fabricated test chip for ReRAM architecture exploration and characterization. The test chip will include multiple distinct ReRAM implementations in one design, resulting in a final chip that can test multiple implementations for research purposes. Ultimately, the final design will be laid out with four distinct architectures and a testbench for component characterization with simulation data demonstrating functionality.

### **1.2 Users and User Needs**

The ISU ECpE faculty and their research teams (grad and undergrad) serve as the main client(s)/user(s) for this project. Secondary users include ChipForge, an Iowa State University club, while tertiary users encompass researchers and enthusiasts outside of our department. The objective of our project is to create a research test chip with multiple ReRAM architectures from past teams, in addition to our own, on the chip. In conjunction with the design of these architectures, comprehensive documentation will be produced to guide users on tool utilization, troubleshooting, and the design process. ISU research faculty will then use the chip to evaluate and characterize the different ReRAM architectures. Providing a finished top-level design, testbenches, and layout will meet the user needs. Additionally, in-depth documentation for the top level design and proposed architectures. To perform sufficient testing on each architecture, the research teams must be able to test and characterize each component individually to verify the functionality of system subcomponents. Along with testbench results, C code must be provided to allow the MCU to interface with the chip, performing testing and measurements.

#### **1.3 What is ReRAM?**

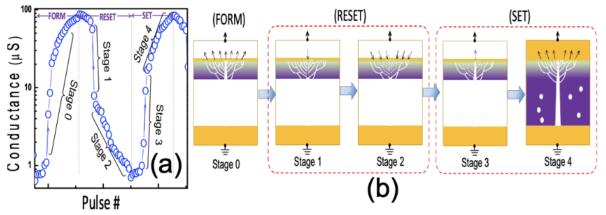

ReRAM is a part of emerging nonvolatile technologies that is aiming to address the limitations of conventional memory systems. ReRAM operates as a resistive switching, where a voltage induces a filament to grow between two electrodes. When the resistive material creates a filament it provides low resistance which entails a one. If the filament is broken then the resistance is high which creates a zero. There are three distinct modes for ReRAM; forming, writing and reading. Forming is when voltage is first applied to the cell to create the initial oxygen filament. Writing is where the filament is changed by the application of the electric field. Lastly, reading is where the resistance of the cell is transformed into binary data.

## 2. Requirements, Constraints, and Standards

## 2.1 Requirements

- Functional Requirements

- Four different ReRAM compute crossbar architectures must be present in the final tapeout

- Two architectures will come from the previous two team's final designs.

- Both read from the bit line, and the source and bit lines are parallel in both designs.

- One utilizes a 4-bit ADC, while the other utilizes a 1-bit ADC

- Two additional architectures will be newly designed by our team

- One will be a true crossbar design, with no transistors; a matrix of memristors

- One will parallelize the source and word lines

- Component circuits are individually characterizable and accessible through analog pins, and include the following:

- One, three, and four bit ADCs

- Transimpedance amplifier

- ReRAM cell(s)

- One, three, and four bit DACs

- Resource Requirements

- Uncertainty evaluation on architectures being implemented; difference between simulated ideal crossbar current and actual within one ADC step

- C Code for the MCU to interface with the ReRAM that enables testing and demonstrates that the ReRAM can compute a MVM within an epsilon tolerance

- Bring-up Documentation for FORMing the ReRAM Cells and characterizing the component circuitry via individual testbenches.

## **2.2 Constraints**

- Must use Efabless open source tools for design process

- Must use Skywater 130nm process

- Must use previous teams' architectures in our final design

- Final layout design must fit inside project wrapper

## **2.3 IEEE Standards**

- *IEEE 1481-2019- IEEE Standard for Integrated Circuit (IC) Open Library Architecture (OLA)*: This is applicable to our project since it specifies how our integrated circuit should be examined using a variety of design automation tools for timing and power consumption.

- *IEEE 1076.4-2000- IEEE Standard VITAL ASIC Modeling Specification*: This standard is relevant to our project because it calls for the testing of an ASIC chip using extremely precise and effective simulation models.

- *IEEE 1149.4-2010- IEEE Standard for a Mixed-Signal Test Bus*: This is relevant to our project since it will have both digital and analog components, and we will need to properly test each one separately and in tandem.

- *IEEE 1364-2005- IEEE Standard for Verilog Hardware Description Language*: Since our project requires us to create Verilog code to facilitate communication between the wrapper and the analog portion, this standard is appropriate for us.

## 2.4 Applicable Courses From ISU Curriculum

- EE 330

- ENGL 314

- EE 230

- EE 465

- EE 435

- CPR E 381

- CPR E 288

# 3. Project Plan

## 3.1 Project Management/Tracking Procedures

We plan on using the agile methodology for managing our project. Since we meet with our advisors every week, we will do one-week sprints where we can give updates on what was accomplished in the past week. We will use GitHub issues to track tasks on our project. We will also be very deliberate when deciding to commit our changes, ensuring that any time we have our project in a state that we want to save or talk about we can look at the corresponding commit.

## 3.2 Task Decomposition

## Task 1: Figure out the tools and research ReRAM functionality

- Installing toolchain

- Demonstrate competency with tools and refine ChipForge tutorials

- Get an analog device through Pre-check

## Task 2: Verify and integrate previous architectures and peripheral circuitry

- Looking at other team's components and testing if they work

- Get the other team's components through pre-check

## Task 3: Research and implement new architures

- Create schematic for new architecture #1

- Create schematic for new architecture #2

- Integrate new architectures into top-level design

## Task 4: Create Final Layout of Design

- Create layout of circuit component testbench

- Add each unique architecture to the layout

- Clear all DRC Errors from the design

- Make sure the design passes LVS

### Task 5: Verify Behavior of Final Design

- Perform post extraction simulation on components

- Perform post extraction simulation on unique architectures

- Verify that simulation results match expected behavior

### Task 6: Get Final Design Through Efabless Checks

- Get final design through Efabless hosted precheck

- Get final design through Efabless hosted tapeout check

### Task 7: Create Bring-up Documentation and C Code

- Write bring-up documentation

- Write accompanying C code for the project

## 3.3 Project Proposed Milestones, Metrics, and Evaluation Criteria

- All of the previous team's modules function as expected

- Post-integration of the previous team's modules function as expected while passing DRC and LVS checks

- We have created our own architectures that function as expected and pass DRC and LVS checks

- All four architectures are integrated and pass DRC, LVS, and precheck

- The component testbench has been integrated and passes DRC, LVS, and precheck

## **3.4 Project Timeline/Schedule**

Figure 3.1: Gantt chart

## 3.5 Risks and Risk Management/Mitigation

- Past team's design does not pass functional tests or pre-check

- **Risk 40% :** Past team's design does not pass functional tests or pre-check. Efabless tools have evolved over time, so past designs may no longer pass verification. Models may have been updated or files may be missing. To prevent a roadblock, we will begin by testing each component individually before integrating any of the designs to catch any problems early on. We may need to re-layout these components if they fail.

- At least one of the new designs does not satisfy the requirements

- **Risk 15% :** There is a lot of potential for noise to interfere with the functionality of our circuits, as well as other various issues that could arise from our component circuitry. To mitigate this, we will make sure to do our research on different design architectures to produce a different process that our clients and end users will benefit from.

- Integrated top-level project wrapper design fails functional tests or pre-check

- **Risk 55%**: Combining all of our components into one cohesive design may provide some issues while running the final checks. To mitigate this issue, we will make sure to run constant LVS and prechecks as we go along the integration process.

## - Flicker noise is more impactful on the Skywater process than expected

- Risk 15%: Finding the necessary values in the Skywater PDK to calculate the corner frequency between flicker noise and thermal noise has not been successful. In terms of simulation, there is not one agreed upon method of simulating flicker noise. Currently, we are unsure of what method our software is using, making simulation results more difficult to interpret. However, for most modern processes, the effects of thermal noise in the megahertz region are much more impactful than that of flicker noise [1]. Additionally, the impedance of the memristor will be much greater than that of any MOS device used in an architecture, so the dominant source of noise in these designs will be the ReRAM cells. To mitigate this potential risk, we can increase the clock speed of our circuit to around 20MHz where thermal noise will certainly be dominant.

## 3.5.1 Updated Risks and Risk Management/Mitigation Post Efabless-Shutdown

Due to Efabless shutdown we had to update a few of our risks.

- Final design is unable to be fabricated

- **Risk 100%:** Due to the efabless shutdown in early march, there is no possibility of our design being fabricated at this time. Despite losing the resources from efabless and their open-source Slack community, we are working through the project to meet our deadlines as if this event did not occur. Working towards our original goal is the best mitigation strategy to reach a successful outcome.

- Past team's design does not pass functional tests or pre-check

- **Risk 100% :** Past team's design does not pass functional tests or pre-check. Efabless tools have evolved over time, so past designs no longer pass verification.

Two of the main reasons for this stem from tool versioning issues, and the ReRAM SPICE file not being able to pass precheck. Models may have been updated or files may be missing. To try and work through roadblocks, we will test each component individually before integrating any of the designs to catch sources of error. We will need to re-layout these components if they fail or did not have a layout to begin with.

## - Integrated top-level project wrapper design fails functional tests or pre-check

- **Risk 100% :** As previously mentioned, the ReRAM cell SPICE model is able to be simulated, but is not able to pass pre-check. This was an issue we planned to work through with the efabless employees, but after the shutdown this was no longer an option. To mitigate this issue, we will make sure that our final design passes both DRC and LVS checks to get as close to achieving our original goal as possible.

## **3.6 Personnel Effort Requirements**

|                                                                              | Time    |

|------------------------------------------------------------------------------|---------|

| Task 1: Figure out the tools and research ReRAM functionality                | 70 hrs  |

| Installing toolchain                                                         | 10 hrs  |

| Demonstrate competency with tools<br>and refine ChipForge tutorials          | 40 hrs  |

| Get an analog device through<br>Pre-check                                    | 20 hrs  |

| Task 2: Verify and integrate previous architectures and peripheral circuitry | 120 hrs |

| Looking at other team's components<br>and testing if they work               | 60 hrs  |

| Get the other team's components through pre-check                            | 60 hrs  |

| Task 3: Research and implement new architures                                | 90 hrs  |

| Create schematic for new architecture #1                                     | 30 hrs  |

| Create schematic for new architecture #2                                     | 30 hrs  |

| Integrate new architectures into top-level design                            | 30 hrs  |

| Task 4: Create Final Layout of<br>Design                                     | 50 hrs  |

| -                                                          |        |

|------------------------------------------------------------|--------|

| Create layout of circuit component testbench               | 20 hrs |

| Add each unique architecture to the layout                 | 20 hrs |

| Clear all DRC Errors from the design                       | 5 hrs  |

| Make sure the design passes LVS                            | 5 hrs  |

| Task 5: Verify Behavior of Final<br>Design                 | 80 hrs |

| Perform post extraction simulation on components           | 20 hrs |

| Perform post extraction simulation on unique architectures | 30 hrs |

| Verify that simulation results match expected behavior     | 30 hrs |

| Task 6: Get Final Design Through<br>Efabless Checks        | 60 hrs |

| Get final design through Efabless hosted precheck          | 30 hrs |

| Get final design through efabless hosted tapeout check     | 30 hrs |

| Task 7: Create Bring-up<br>Documentation and C Code        | 40 hrs |

| Write bring-up documentation                               | 20 hrs |

| Write accompanying C code for the project                  | 20 hrs |

Table 3.1: Personnel effort requirements

## **3.7 Other Resource Requirements**

All of the CAD tools are open-source software. However, the software that will be used is not well documented so we have to rely heavily on previous teams documentation and tutorials. The other resources are used to create schematics and layouts and test the functionality of the components and circuits. These resources include:

- Xschem: Schematic capture

- Magic: Layout

- Netgen: LVS

- Slack: online community for help with open source toolset

We also have access to the lab in Durham 310, which has FPGAs that we can use through their comparch computer. We may need to design a PCB breakout board once our design is fabricated, for which we can use ChipForge documentation. Finally, we have \$9,750 for the

ReRAM Efabless tapeout for ChipIgnite 2504, which is provided to us by our client, Dr. Duwe, through an NSF award.

## 4. Design

## 4.1 Broader Context

## 4.1.1 Broader context

The test chip is designed for the research and engineering community. This chip will explore the next-generation of in compute memory. The communities that are being affected by this design are data-intensive industries such as healthcare, finance, autonomous systems, and machine learning will benefit from the reduced energy consumption associated with ReRAM compute in memory systems. Lastly, the societal needs that our project addresses are energy efficiencies and technological advancement which create competitiveness in the future for technology.

| Area                                     | Description                                                                                                                                                                                                                                          | Examples                                                                                                                                                                                                                                   |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Public Health,<br>Safety, and<br>Welfare | The ReRAM test chip will<br>demonstrate computational efficiency<br>potentially reducing energy<br>consumption of artificial intelligence<br>machine learning. This can benefit<br>communities by lowering energy<br>demand and associated emissions | Reducing energy consumption<br>would decrease greenhouse gas<br>emissions which will improve the<br>quality of the air in areas with<br>significant computational<br>infrastructure.                                                       |

| Global,<br>Cultural, and<br>Social       | By advancing energy-efficient<br>technology, this project aligns with<br>the global efforts towards sustainable<br>and energy reductions, valued by<br>diverse and professional communities.                                                         | The project supports globe<br>sustainability initiatives by<br>reducing the carbon footprint of<br>computational operations.                                                                                                               |

| Environmental                            | ReRAM aims to reduce energy<br>consumption and create low powered<br>technologies compared to traditional<br>memory. However, the fabrication<br>process might use hazardous material,<br>so that effect is unknown.                                 | While the energy usage during the<br>operation of the ReRAM<br>compute-in-memory systems is<br>reduced. The manufacturing<br>process of the ReRAM cells, such<br>as transition metal oxide, must be<br>evaluated to ensure sustainability. |

| Economic                                 | The cost of this device may be<br>expensive at first but it creates a more<br>energy efficient outcome. In the long<br>run it will make                                                                                                              | Successful implementations of<br>ReRAM compute-in-memory<br>systems will create job<br>opportunities in low-power<br>hardware design and<br>manufacturing.                                                                                 |

### **4.1.2 Prior Work/Solutions**

Since ReRAM is an emerging technology, especially for compute purposes, there are no commercially available solutions on the market. We have looked closely, of course, at the previous two senior design team's projects for reference. In addition, the ISAAC design is an example of an academic implementation of a ReRAM-based true machine learning accelerator. The table below lists pros and cons of each of these designs, as well as our design.

| Product                                  | Pros                                                                                                                                                                                                                       | Cons                                                                                                                                                                                                         |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ISAAC ReRAM-based CNN<br>Accelerator [3] | <ul> <li>Acts as a true AI accelerator</li> <li>Uses 1T1R grid for more precise memristor writes</li> <li>Shared ADC allows for better precision</li> </ul>                                                                | <ul> <li>Shared ADC requires<br/>sample and hold<br/>circuits</li> <li>Very specialized to<br/>one application, not as<br/>general for research</li> </ul>                                                   |

| Design made by sddec23-08                | <ul> <li>Uses 1T1R grid for<br/>more precise<br/>memristor writes</li> <li>Multiple ADCs; one<br/>for each read line</li> </ul>                                                                                            | <ul> <li>Multiple ADCs = less<br/>precision (1 bit)</li> <li>Only includes one<br/>ReRAM architecture</li> </ul>                                                                                             |

| Design made by sddec24-13                | <ul> <li>Uses 1T1R grid for<br/>more precise<br/>memristor writes</li> <li>Shared ADC allows<br/>for better precision</li> </ul>                                                                                           | <ul> <li>Shared ADC requires<br/>sample and hold<br/>circuits</li> <li>Only includes one<br/>ReRAM architecture</li> </ul>                                                                                   |

| Our design                               | <ul> <li>Includes four<br/>individually accessible<br/>unique ReRAM<br/>architectures</li> <li>Includes individually<br/>characterizable<br/>component circuitry</li> <li>Generalized for<br/>research purposes</li> </ul> | <ul> <li>Research-focused,<br/>unlikely to be useful<br/>in a true machine<br/>learning context</li> <li>Could suffer from<br/>over-complication<br/>since it includes many<br/>different designs</li> </ul> |

Table 4.2: Pros/Cons of prior work/solutions

#### 4.1.3 Technical Complexity

Our design presents a variety of technical challenges:

- 1. Since we are using open source software, none of our team members are familiar with the tools we are using. This provides a barrier of entry to getting started with our actual design.

- 2. ReRAM is an emerging technology, and there are very few opportunities available for fabrication of ReRAM chips. Also, there is little information about ReRAM usage for compute-in-memory applications, so we are exploring a new frontier.

- 3. We are including four different ReRAM architectures in our design, which of course increases the complexity of our design. However, this will likely help us down the line: if we find that one of our architectures doesn't work as intended, there are still three others to test.

- 4. We are also integrating a number of components acting as the peripheral circuitry of the design. This includes S&H circuits, TIAs, DACs, and ADCs. While our team doesn't have direct experience with each of these components, they are very well studied in academia and in industry, so finding documentation about them shouldn't be a struggle.

## 4.2 Design Exploration

### 4.2.1 Design Decisions

### 1. New ReRAM Architectures

The first design decision we had to make was what kinds of crossbars we would use in our unique ReRAM architectures. For our first crossbar, we decided to do a similar 1T1R matrix as the two senior design teams that came before us, but ours would be different by parallelizing the bitlines and sourcelines in our layout. The previous two teams had their sourcelines parallel to their wordlines. We decided to change things up with our second crossbar design and explore a true ReRAM crossbar, which uses no transistors and only uses a matrix on ReRAM cells. We felt that this would offer a unique solution that maximizes density within our crossbar. The operations on this crossbar are more difficult and noise-prone, but the potential for high-density ReRAM computation could be worth the risk.

#### 2. ADC Resolution

We had a few options for ADC resolution in our project. We could use the 1-bit ADC from team sddec23-08, the 4-bit ADC from team sddec24-13, or design our own new ADC at a different resolution. We were partly swayed in our decision due to verification difficulties with the 4-bit ADC (seemingly due to differences in our tool installations), but we ended up using the 1-bit ADC in our design. The advantage to this decision is that each bitline has its own ADC, so there is no need for additional circuitry for sharing a single ADC among each line. This simplistic nature should work well for a research chip that is more for proving the concept than getting precise results.

### 3. Multiplexing Outputs

The next major design decision came when integrating all of our designs and our component testbench into our top level schematic. The user needs a way to choose which architecture to get output from, since there are not enough pins in the Caravel wrapper to connect to all of our architectures and component circuit testbenches. So, we designed a multiplexing circuit that takes in two select lines for choosing between our four architectures, as well as an additional select line for choosing whether the output should come from the architectures or the component testbench. The user can then change the values of these select lines depending on their desired output. The logic analyzer output will always be from one of our crossbar architectures or the component testbench.

#### 4.2.2 Ideation

One of the key uncertainties in our design process is whether we will be able to achieve precise and accurate data retrieval from the output line. Currently, we are still in the process of determining the length of the interconnects and assessing the level of noise that must be accounted for when acquiring data from the output. This is why the selection of an appropriately designed Analog-to-Digital Converter (ADC) is critical to the success of the project. The ADC choice will not only determine whether the project is feasible but will also play a crucial role in ensuring the functionality and scalability of the system in the broader context of the project. This includes the goal of enhancing the performance of AI accelerators by reducing power consumption and improving processing speed.

Additionally, we are reviewing the designs developed by our previous team, with the possibility of incorporating elements of their architecture into our own designs. Their work includes the use of a 4-bit Flash ADC and a Sample-and-Hold (S&H) ADC, both of which provide useful insights and potential integration points for our architectures. Below are five potential ADC design approaches that we are considering in our two architectures.

- Current\_Mode ADC

- 4-bit Flash ADC

- 1-bit S&H ADC

- Delta Sigma ADC

- Pipeline ADC

#### 4.2.3 Decision-Making and Trade-off

Below is a table that weighs the benefits and drawbacks of each ADC design. With the use of this table and previous designs, we will choose whether we want to implement a new ADC within our designs that differentiates from the previous teams or utilize one of theirs.

| Architecture Type         | Pros                                                                                            | Cons                                                                                                                                  |

|---------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Current-Mode ADC          | It can handle small variations<br>in current levels and use low<br>power consumption.           | Susceptible to small amounts<br>of noise and low resolution<br>compared to other ADC<br>designs.                                      |

| 4-bit Flash ADC           | Fast conversions as well as simplicity in design with ideal parallel processing.                | High power consumption as<br>well as large area and<br>susceptible to noise<br>environments.                                          |

| 1-bit sample and hold ADC | Extremely fast conversions,<br>extremely low power<br>consumption, and simplicity<br>in design. | Only limited to binary<br>decision-making, not suitable<br>for high precision<br>applications, and sensitive to<br>noise.             |

| Delta Sigma ADC           | Very high resolution with<br>exceptional precision and<br>accuracy. Great noise<br>reduction.   | Very slow and has higher<br>power consumption compared<br>to other ADC designs.                                                       |

| Pipeline ADC              | High speed with fast<br>conversion rates, making it<br>useful for high-speed<br>applications.   | More complex than other<br>ADC designs and has high<br>power consumption. It may<br>lack high resolution based on<br>the application. |

Table 4.3: Comparing ADC architectures

We also needed to explore pros and cons for different ReRAM crossbar architectures. Below is a table to visualize the positives and negatives of each design.

| Crossbar Type                             | Pros                                                                                                                            | Cons                                                            |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| 1T1R grid, parallel word and source lines | Transistors make it easier to select individual cells for operations                                                            | Less dense                                                      |

| 1T1R grid, parallel bit and source lines  | Transistors make it easier to<br>select individual cells for<br>operations, also able to test an<br>additional layout for noise | Less dense, need to create and<br>verify an entirely new layout |

| True crossbar                             | Higher density                                                                                                                  | More overhead for operations                                    |

Table 4.4: Comparing ReRAM crossbar architectures

### 4.3 Proposed Design

#### 4.3.1 Overview

Our design aims to characterize four unique matrix-vector multiplication modules that utilize ReRAM for performing compute-in-memory operations. These modules will consist of component circuitry, the first of which is the ReRAM crossbar itself. The ReRAM crossbar is a matrix of ReRAM cells where the actual computation will take place. Another component circuit is the trans-impedance amplifier (TIA), which will convert currents into voltages which will represent the result of the operation. The final major component circuit is the ADC, which will convert our analog result into a digital value readable by the CPU. Each component circuit will be individually characterizable as part of our design as well.

#### 4.3.2 Detailed Design and Visuals

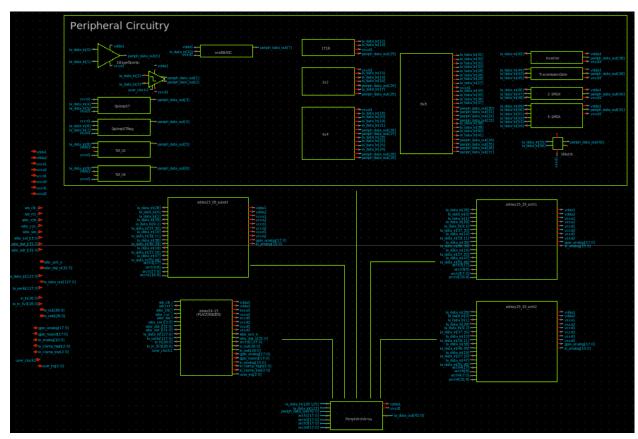

The goal of this design is to combine four different ReRAM crossbar architectures into one top-level block design. These will all be connected to the microcontroller via Logic Analyzer Pins, which are responsible for communication between the microcontroller and the ReRAM crossbar systems, such as reading values from the current crossbar or sending values to it. Two of the ReRAM crossbars will be sourced from the previous teams' designs, while the other two will be original designs. The original designs should closely resemble the previous designs, with minor architectural changes, such as swapping the directions of the source and bit lines. The top-level design should also include separate, individually characterizable testbenches for the different types of peripheral circuitry, including the ADC, DAC, and TIA. The top-level diagram outlines the design, while a lower diagram presents a potential internal design for a ReRAM crossbar. The ReRAM crossbar consists of a matrix of ReRAM cells connected by lines called bit lines, source lines, and word lines. The matrix, and input values are sent into the matrix via either the bit line or the source line, depending on the specific architecture. The previous teams' designs should be used in depth as references when designing the new architectures.

Figure 4.1: Top level block design

Figure 4.2: Schematic for one ReRAM crossbar architecture

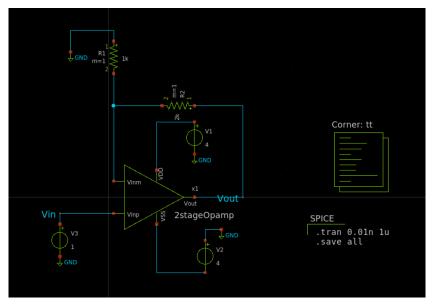

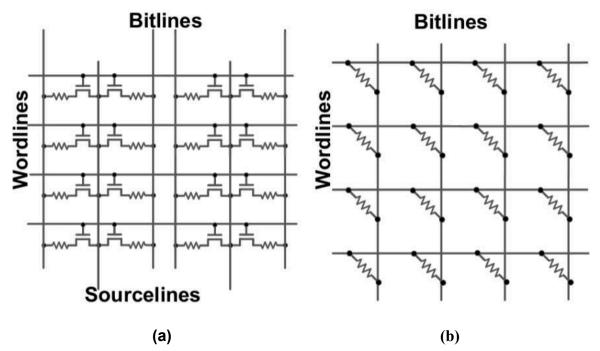

Figure 4.3: Schematic for our final top level design

Our top level schematic matches up well with our original vision that we created in our block diagram. It consists of our four architectures and our component/peripheral circuitry testbench area, all connected to a multiplexer that determines our final output.

|                                    |                                                 | ×20 · · · · · · · · · |

|------------------------------------|-------------------------------------------------|-----------------------|

|                                    | sddec23_08_subckt                               |                       |

| la data in[28] Write_S             | elect_8LineBitinput_2 vdda1                     | vddal                 |

|                                    | elect_8LineBitinput_1 vdda2                     | - vdda2               |

| la data in[1] Write F              | orm Select 8LineBitinput 1 vssa1                | vssal                 |

| la data in[29] Write F             | orm_Select_8LineBitinput_2 vssa2                | vssa2                 |

| la data in[9:2] IAIN 8             | UneBitinput_1[7:0] vccd1                        | vccdl                 |

|                                    | UneBitinput_2[7:0] vccd2                        | vccd2                 |

|                                    | elect 8LineWordInput 1 vssd1                    | vssd1                 |

| la data in[18:11] 📖 🛚              | LineWordInput_1[7:0] vssd2                      | - vssd2               |

|                                    | elect_8LineWordInput_2 gplo_analog[17:0]        | gpio analog[17:0]     |

| la data in[46:39] 14 IN 8          | UneWordInput_2[7:0] io_analog[10:0]             |                       |

|                                    | Selectinput_1                                   |                       |

| la data in[27:20] 14_1N_8          | UneSelectinput_1[7:0]                           |                       |

|                                    | Selectinput_2                                   |                       |

|                                    | LineSelectinput_2[7:0]                          |                       |

| arch1[17] vssneg                   | 8LineSelectOutput04                             |                       |

| arch1[8] vssneg                    | 8LineSelectOutput02                             |                       |

| arch1[7:0] u.our                   | 8LineSelectOutput02[7:0]                        |                       |

| arch1[16:9] 🗤 our                  | 8UneSelectOutput04[7:0]                         |                       |

|                                    |                                                 |                       |

|                                    |                                                 |                       |

|                                    |                                                 |                       |

|                                    |                                                 |                       |

|                                    |                                                 |                       |

| wbiclk i 🛥                         | wb_dk_l vdda1 vdda1                             |                       |

| wb_cik_i                           | wb_rst_l · · · · · · vdda2 - vdda               | _                     |

| wb_ist                             | wbs_stb_l · · · sddec24-13 · · vssa1 · · · vSsa | -                     |

| wbs_stb_i                          | wbs_cyc_1: (PLACEHOLDER) vssa2                  |                       |

| wbs-we-i                           | wbs.weil vccdi vccdi                            |                       |

| wbs sel i[3:0]                     | wbs_sel_[[3:0].                                 |                       |

| wbs_sci_[[5:0]                     | wbs_dat_[[31:0]                                 |                       |

| wbs_ddt_[[31:0]                    | wbs_adr_l[31:0] · · · · · · · vssd2 · · · vssd2 |                       |

| la data in[127:0]                  |                                                 | acko                  |

| la oenb[127:0]                     |                                                 | dat o[31:0]           |

| io in[26:0]                        |                                                 | 2[127:0]              |

| io in 3v3[26:0]                    |                                                 | rt[26:0]              |

| user clock2                        |                                                 | eb[26:0]              |

| · · · · · · · <del>·</del> · · · · |                                                 | analog[17:0]          |

|                                    |                                                 | noesd[17:0]           |

|                                    |                                                 | nalog[10:0]           |

|                                    |                                                 | amp high[2:0]         |

|                                    |                                                 | amp low[2:0]          |

|                                    |                                                 | irg[2:0]              |

|                                    |                                                 |                       |

|                                    |                                                 |                       |

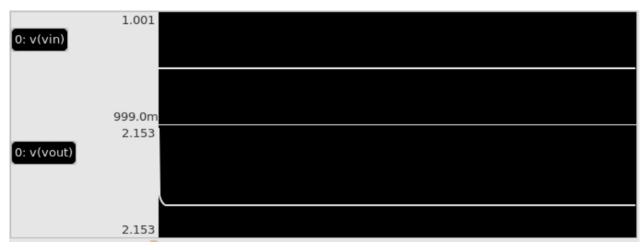

Figure 4.4: Architectures from SDDec38-08 and SDDec24-13 in our top level design

Two of our four unique architectures were designed by the previous two teams. They both used the same crossbar architecture, but their designs differed in peripheral circuitry. Team sddec23-08 used a 1-bit ADC, while one of sddec24-13's major contributions was a 4-bit ADC. Due to this difference, the design with the 4-bit ADC shared a single ADC among each bitline, while the other design had individual ADCs for each bitline.

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | x1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| in the data in [201 H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| la data in[28]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Write_Select_8UneBitmput_2 vida1 vida1 vida1 vida2 vida2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| la data in[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Write Form Select 8UneBitinput 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |