# ASIC ReRAM Compute Test Chip

#### Team sdmay25-19

By: Noah Mack, Olivia Price, Travis Jakl, Sam Burns Clients/Advisors: Dr. Henry Duwe and Dr. Cheng Wang

### Problem Statement

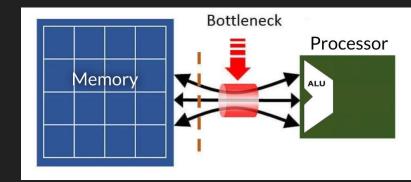

- AI is growing in demand, and right now it's an energy intensive process

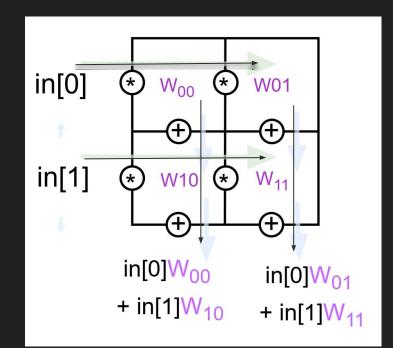

- Matrix-vector multiplication (MVM) is crucial in machine learning

- Data transfer between memory and CPU creates bottlenecking

- What can be done about this?

Source [1]

2

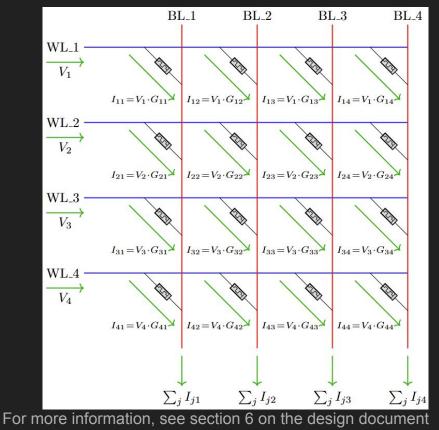

# **Compute-In-Memory**

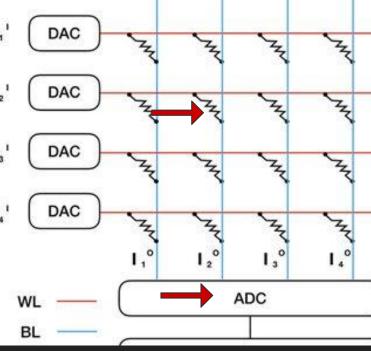

- MVM is performed within memory system

- Alleviates bottleneck between memory and CPU

- Works via multiply and accumulate process

- Many technologies for this system

- Resistive Memory (ReRAM)

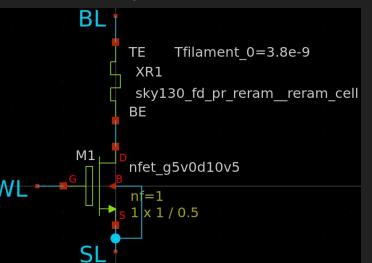

# What is ReRAM?

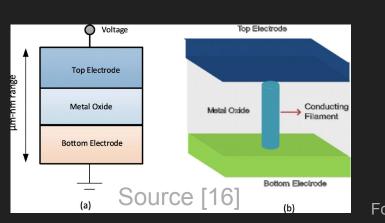

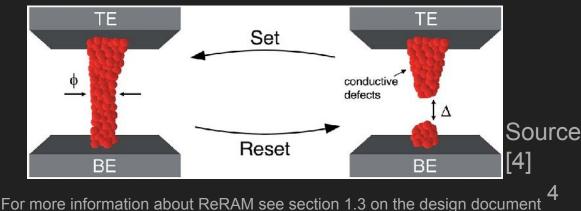

- Non-volatile memory technology, that is presently used for storing memory

- Filament formation controls current flow

- High and low conductance states

- By abusing the ReRAM we can allow for analog computation

#### Noise

- Since we are abusing ReRAM, there will be a lot of noise

- Other components in the design that will <sup>a</sup> cause noise in the designs include:

- ADC (differential nonlinearity noise)

- Bitline or word line

- Transistor (minimal)

- TIA

- Researchers need to better understand the characterization of noise

### **Our Solution**

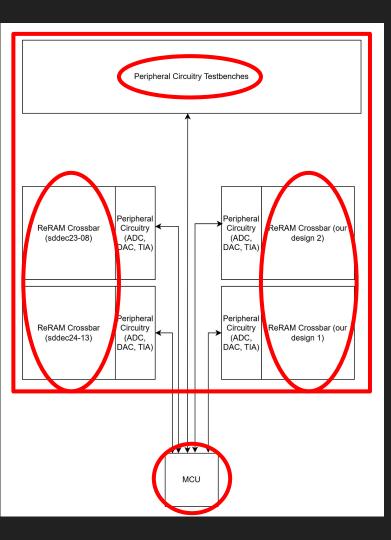

- Design a test chip with four unique ReRAM-based compute-in-memory architectures to allow us to understand how the noise will affect circuitry.

- Use Skywater 130nm process and Efabless tools for fabrication and tape-out

#### efabless Source [3]

#### Users

Primary Users:

- ISU ECpE faculty and research teams (graduate and undergraduate).

Secondary Users:

- ChipForge: An Iowa State University club that started this semester

- Students in CPRE 4870/5870, EE 5260

Tertiary Users (Public):

- Public (which will further research in the field and help the field evolve)

#### Requirements

### Requirements

- Four different ReRAM compute crossbar architectures

- Different configurations of source, bit, word lines

- Different peripheral circuitry

- True crossbar vs. 1T1R grid

- Component circuits are individually characterizable and accessible through external analog I/O

- Uncertainty evaluation for implemented architectures

- Crossbar noise

- ADC noise

- Design for worst case crossbar noise within one ADC step

### Requirements

- Bring-up Documentation and code for validation and debug

- Characterizing the component circuitry via individual test benches.

- FORMing the ReRAM cells

- C Code for the MCU to interface with the ReRAM that enables testing and demonstrates that the ReRAM can compute an MVM within an epsilon tolerance.

#### Designs

# Top Level Design

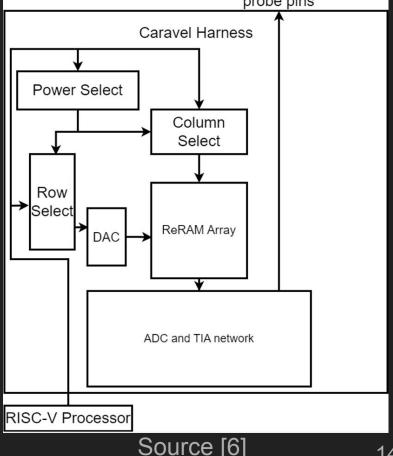

### Team sddec23-08

- Pioneered the tools used in this project

- Provided tool documentation

- ReRAM Architecture

- One bit sample & hold ADC

- DAC

- TIA

- Read from Source Line

### Team sddec24-13

Output for probe pins

- Added to tool documentation

- ReRAM Architecture

- Four bit flash ADC

- DAC

- TIA

- Strong Arm Comparator

- Read from Source Line

# Our Team sdmay25-19

- New Architecture 1

- Parallelize the source and bit lines

- 4-bit ADC

- Read from source line

- Reduce noise on word lines

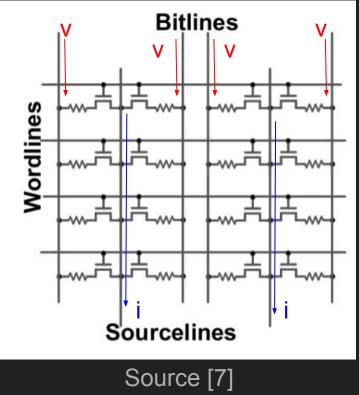

# Our Team sdmay25-19

- New Architecture 2

- True crossbar (no transistors)

- 1-bit ADCs

- Increases density

- More susceptible to noise

#### Risks

- Taped-out chip does not perform as expected

- Risk: 65%

- Past team's design does not pass pre-check

- Risk: 100%

- Integrated top-level wrapper design fails pre-check

- Risk: 55%

- Flicker noise is more impactful on the Skywater process than expected

- Risk: 15%

# **Risk Mitigation**

- Dedicate time towards verifying and adapting past teams architectures

- Pre-layout & post-layout simulation

- Pre-check

- Perform thorough background research to inform design decisions

- Create testbenches and detailed simulations

- Follow proper layout practices for a space efficient designs

- Increasing clock speed into the MHz region decreases flicker noise

- Reach tape-out readiness early

- Talk with eFabless if necessary

#### Resources/Tools

Source [8]

#### - Netgen

#### Testing

# Unit Testing Workflow

- 1. Create schematic testbench using XSchem

- 2. Simulate schematic using Ngspice

- 3. Create layout schematic using Magic

- 4. Extract SPICE netlist from layout

- 5. Simulate layout netlist using Ngspice

- 6. Perform LVS check using Netgen

# **Other Testing Strategies**

Source [12]

Source [14]

- Integration

- Regression Testing

- Acceptance Testing

- Complete by April 21st

Source [13]

# **Bring-up Testing**

- Provide testing strategies in bring-up documentation

- Properly form ReRAM cells

- Verify peripheral circuitry function

- Testing practices for each architecture

### Results

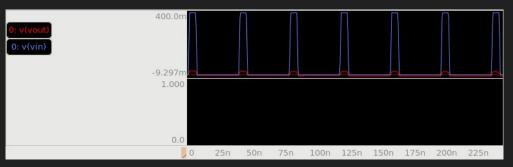

- Testing work of team sddec23-08

- Many components work

- Some need updating

- Same process will occur with team sddec24-13 work

Figure 5.7: Resulting waveforms from 4-to-1 multiplexer testbench from team sddec23-08

Figure 5.5: Resulting waveforms from buffer testbench from team sddec23-08

For more information, see section 5.8 on the design document

#### Results

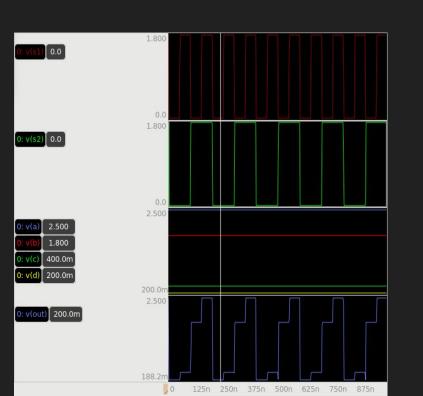

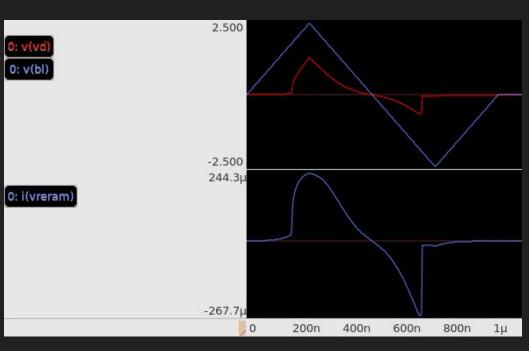

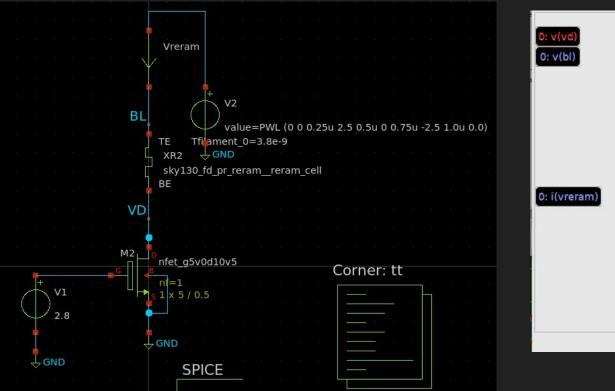

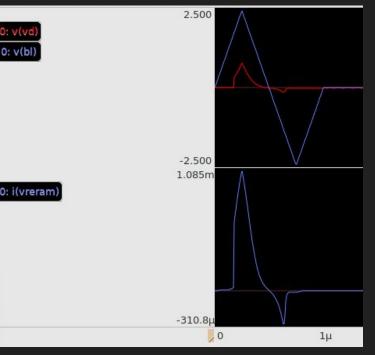

- We have also tested a 1T1R cell (pre-layout sim)

- Perform Set and Reset Operations

Figure 5.10: Waveforms from our 1T1R testbench

#### Results

#### **First Semester Timeline**

| Task Decomposition                                                           | September | October | November | December |  |

|------------------------------------------------------------------------------|-----------|---------|----------|----------|--|

| Task 1: Figure out the tools and research ReRAM functionality                |           |         |          |          |  |

| Installing toolchain                                                         |           |         |          |          |  |

| Demonstrate competency with tools and refine ChipForge tutorials             |           |         |          |          |  |

| Get an analog device through Pre-check                                       |           |         |          |          |  |

| Task 2: Verify and integrate previous architectures and peripheral circuitry |           |         |          |          |  |

| Looking at other team's components and testing if they work                  |           |         |          |          |  |

| Get the other team's components through pre-check                            |           |         |          |          |  |

| Task 3: Research and implement new architures                                |           |         |          |          |  |

| Create schematic for new architecture #1 parallelize with #2                 |           |         |          |          |  |

| Create schematic for new architecture #2                                     |           |         |          |          |  |

| Integrate new architectures into top-level design                            |           |         |          |          |  |

#### Second Semester

| Task Decomposition                                        | January | February | March | April | May |

|-----------------------------------------------------------|---------|----------|-------|-------|-----|

| Task 4: Create Final Layout of Design                     |         |          |       |       |     |

| Create layout of circuit component testbench              |         |          |       |       |     |

| Add each unique archiectecure to the layout               |         |          |       |       |     |

| Clear all DRC Errors from the design                      |         |          |       |       |     |

| Make sure the deisgn passes LVS                           |         |          |       |       |     |

| Task 5: Verify Behavior of Final Design                   |         |          |       |       |     |

| Perfrom post extraction simulation on componnets          |         |          |       |       |     |

| Perform post extraction simulation on unique architecures |         |          |       |       |     |

| Verify that simulation results match expected behavior    |         |          |       |       |     |

| Task 6: Get Final Design Through Efabless Checks          |         |          |       |       |     |

| Get final design through efabless hosted precheck         |         |          |       |       |     |

| Get final design through efabless hosted tapeout check    |         |          |       |       |     |

| Task 7: Create Bringup Documentation and C Code           |         |          |       |       |     |

| Write bringup documentation                               |         |          |       |       |     |

| Write accompanying C code for the project                 |         |          |       |       |     |

### Conclusions

- Familiarize ourselves with analog toolflow

- Tested sddec23-08 components

- Identified working & faulty components

- Found that design does not pass pre-check

- Created own testbenches for 1T1R cell

- Device operates in triode region

- Demonstrates SET and RESET operations

- Planned two unique ReRAM architectures

- Parallelize bit and source lines in 1T1R grid

- True crossbar

# Questions?

# Image Sources

[1] <u>https://www.linkedin.com/pulse/memory-bottleneck-ali-farahany/</u>

- [2] <u>https://skywater-pdk.readthedocs.io/en/main/</u>

- [3] <u>https://efabless.com/</u>

- [4] https://pubs.rsc.org/en/content/articlehtml/2019/fd/c8fd00106e

- [5] https://sddec23-08.sd.ece.iastate.edu/final\_presentation.pdf

[6] https://sddec24-13.sd.ece.iastate.edu/SDDEC24\_13\_DESIGN\_DOCUMENT%20(2).pdf

[7] C. Xu et al., "Overcoming the challenges of crossbar resistive memory architectures," 2015 IEEE 21st International Symposium on High Performance Computer Architecture(HPCA), Burlingame, CA, USA, 2015, pp. 476-488, doi: 10.1109/HPCA.2015.7056056.

#### [8] <u>https://marketplace.visualstudio.com/items?itemName=barakh.vscode-</u> <u>xschem-viewer</u>

# Image Sources

[9] http://opencircuitdesign.com/magic/

[10] https://commons.wikimedia.org/wiki/File:Gtkwave\_256x256x32.png

[11] https://1000logos.net/slack-logo/

[12] <u>https://www.dreamstime.com/photos-images/adding-puzzle-pieces.html</u>

[13] <u>https://www.vectorstock.com/royalty-free-vector/puzzle-pieces-together-vector-14398401</u>

[14] https://www.vectorstock.com/royalty-free-vector/colorful-puzzle-vector-6821228

[15] <u>https://info.efabless.com/chipignite-v2</u>

#### Image Sources

[16] <u>https://link.springer.com/article/10.1186/s11671-020-03299-9</u>

[17]

https://www.researchgate.net/figure/Resistive-random-access-memory-ReRAM-cr ossbar-structure-with-bitlines-BLs-and\_fig2\_360786529